- 您现在的位置:买卖IC网 > Sheet目录3873 > PIC18F13K50-I/P (Microchip Technology)IC PIC MCU FLASH 4KX16 20-PDIP

PIC18F/LF1XK50

DS41350E-page 16

Preliminary

2010 Microchip Technology Inc.

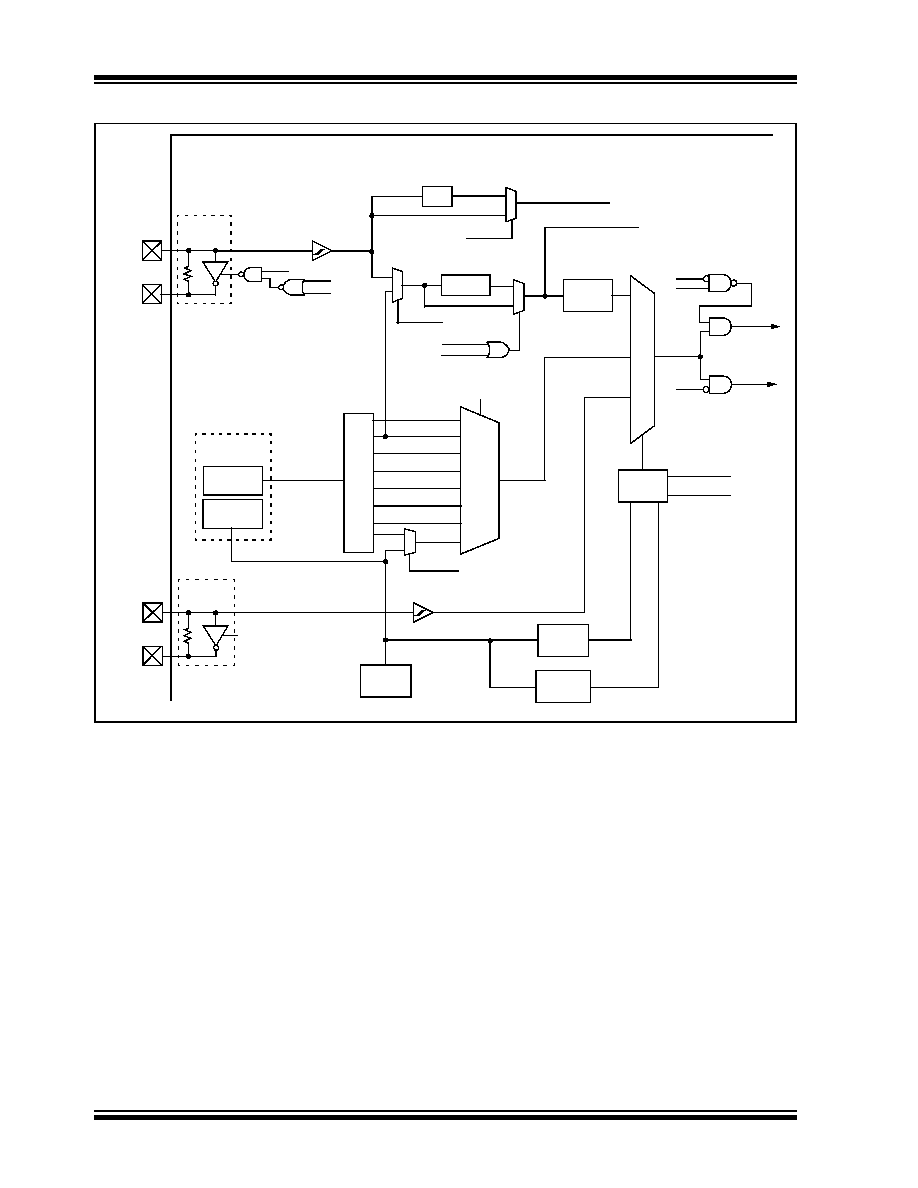

FIGURE 2-1:

PIC MCU CLOCK SOURCE BLOCK DIAGRAM

4 x PLL

FOSC<3:0>

OSC2

OSC1

Sleep

CPU

Peripherals

IDLEN

P

o

stscale

r

MU

X

MU

X

16 MHz

8 MHz

4 MHz

2 MHz

1 MHz

250 kHz

500 kHz

IRCF<2:0>

111

110

101

100

011

010

001

000

31 kHz

LFINTOSC

Internal

Oscillator

Block

Clock

Control

SCS<1:0>

HFINTOSC

16 MHz

0

1

INTSRC

Primary

PIC18F/LF1XK50

Sleep

System

Secondary

T1OSCEN

Enable

Oscillator

T1OSI

T1OSO

PCLKEN

PRI_SD

2

CPU

Divider

0

1

0

USBDIV

FOSC<3:0>

Low Speed USB

High Speed USB

PLLEN

SPLLEN

Oscillator

Watchdog

Timer

Oscillator

Fail-Safe

Clock

Two-Speed

Start-up

Clock

00

1x

01

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16CR76T-I/SO

IC PIC MCU 8KX14 28SOIC

PIC18LF24K22-I/MV

IC PIC MCU 16KB FLASH 28UQFN

PIC18LF24K22-I/ML

IC PIC MCU 16KB FLASH 28QFN

PIC16CR76T-I/ML

IC PIC MCU 8KX14 28QFN

PIC16F627-04/P

IC MCU FLASH 1KX14 COMP 18DIP

PIC18F45J10-I/ML

IC PIC MCU FLASH 16KX16 44QFN

PIC18F24K22-I/ML

IC PIC MCU 16KB FLASH 28QFN

PIC16CR76-I/SS

IC PIC MCU 8KX14 28SSOP

相关代理商/技术参数

PIC18F13K50-I/P

制造商:Microchip Technology Inc 功能描述:20 Pin 8 KB Flash 512 RAM 15 I/O 10

PIC18F13K50-I/SO

功能描述:8位微控制器 -MCU 8KB Flash 512 RAM 15 I/O 10-B ADC USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F13K50-I/SO

制造商:Microchip Technology Inc 功能描述:20 Pin 8 KB Flash 512 RAM 15 I/O 10

PIC18F13K50-I/SS

功能描述:8位微控制器 -MCU 8KB Flash 512 RAM 15 I/O 10-B ADC USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F13K50-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC18F13K50T-I/SO

功能描述:8位微控制器 -MCU 8KB Flash 512 RAM 15 I/O 10-B ADC USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F13K50T-I/SS

功能描述:8位微控制器 -MCU 8KB Flash 512 RAM 15 I/O 10-B ADC USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F14K22-E/ML

功能描述:8位微控制器 -MCU 16KBFlash 512byteRAM 256bytesEEPROM

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT